次10奈米世代的半導體怎麼做?

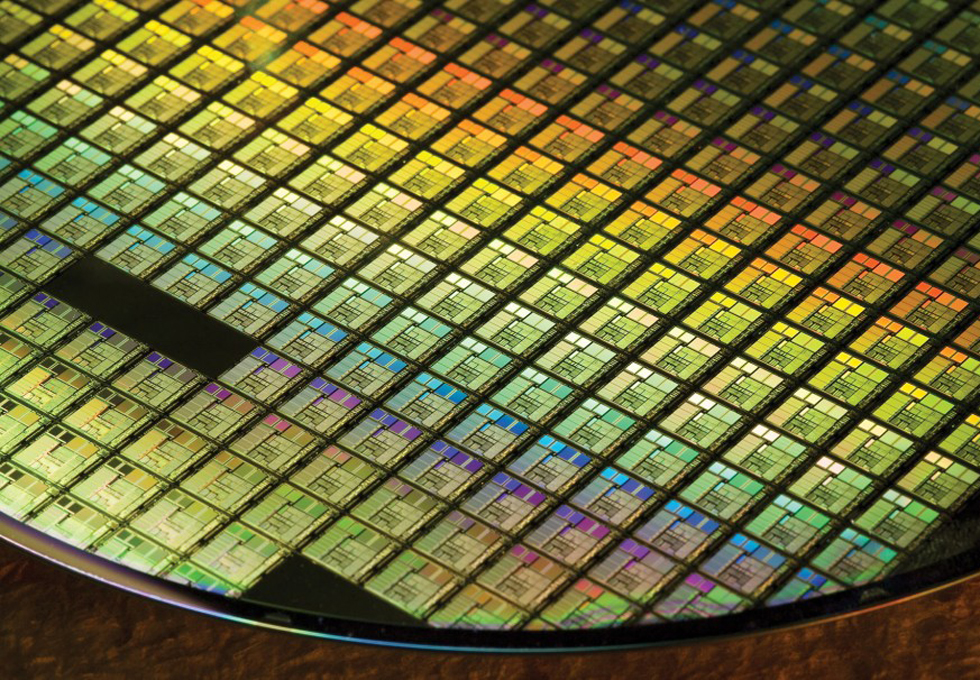

■在相同的區域放入越多的電子元件,代表同一支手機或電腦裝置能提供更強更快速的服務,因此縮小處理器中電子元件的尺寸是所有半導體大廠共同的目標。能依照國際半導體技術藍圖(ITRS)提升製造能力的公司將能獨佔市場,就像台積電排除三星公司,將在2017和2018年連續獨佔蘋果iPhone手機處理器。若要在未來的半導體節點持續保持領先,科技必須與時俱進。在這個10奈米節點以下的世代,各家製造商正積極尋求增加單位面積上電路效能的方法。

撰文|陳奕廷

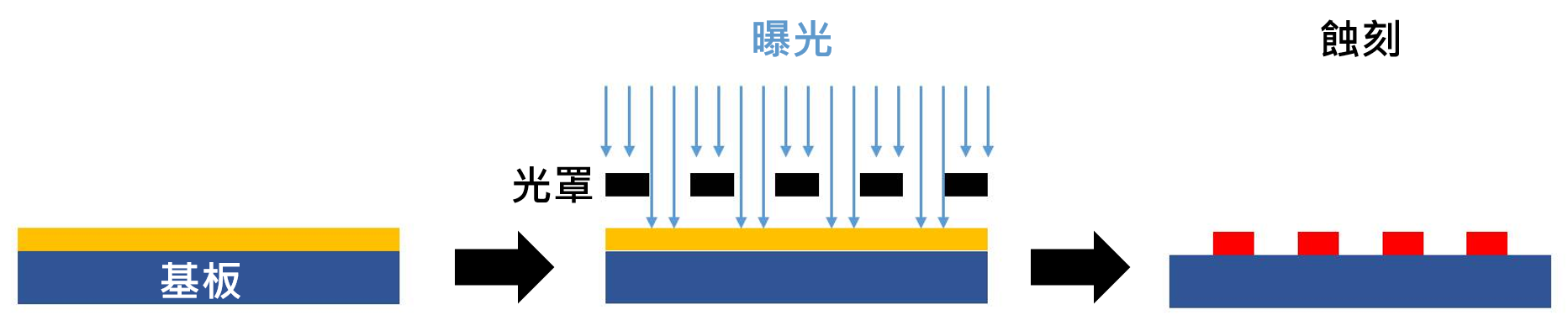

幾乎自從電晶體被發明以來,人們即開始使用「曝光-蝕刻」的方式製作半導體元件:如圖一所示,基板上有待蝕刻的半導體材料(圖一左,黃色)。工程師將想要製作的電路圖案畫在光罩上,並讓材料曝曬光線(圖一中)。沒有曝光的區域非常容易被蝕刻,而接受曝光的區域變得屹立不搖,經過蝕刻之後能留下來。如此一來,工程師將原本在光罩上面的電路圖形轉移到半導體上面(圖一右,紅色)。

單一電晶體的半導體物理特性對於縮小尺寸也很重要,但本文主要針對曝光蝕刻科技,介紹一些在10奈米以下半導體節點的重要或潛在技術。

●浸潤式蝕刻 (immersion lithography)

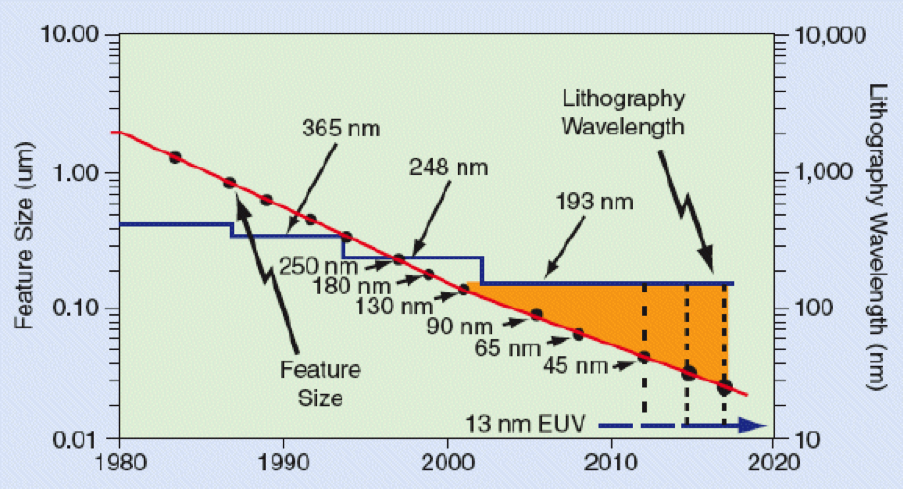

我們僅僅需要將光罩的圖案越畫越小,就能蝕刻出越來越小的電路。但是當光罩的尺寸和光源的波長差不多小的時候,繞射效應變得相當嚴重,曝光出來的電路和光罩上圖案相差非常大。要解決這個問題,使用更小的波長就好了。從原本的綠光顯影,波長一路降將低到藍光、甚至紫外光。然而,波長越短的光成本越高,而且紫外光具有高能量,很容易將許多元件直接打壞,半導體製程曾經因此卡住無法繼續微縮。時任台積電研發副總的林本堅博士發明了浸潤式蝕刻,一舉打破了波長的限制。光在液體中跑得慢,波長也短。利用這個原理,把晶圓泡在液體中就在相同的光源下,使晶圓看的等效波長變小,製作出更小的結構。自從65奈米節點,浸潤式蝕刻被廣泛使用在製程之中。

●多重曝光(multiple patterning)

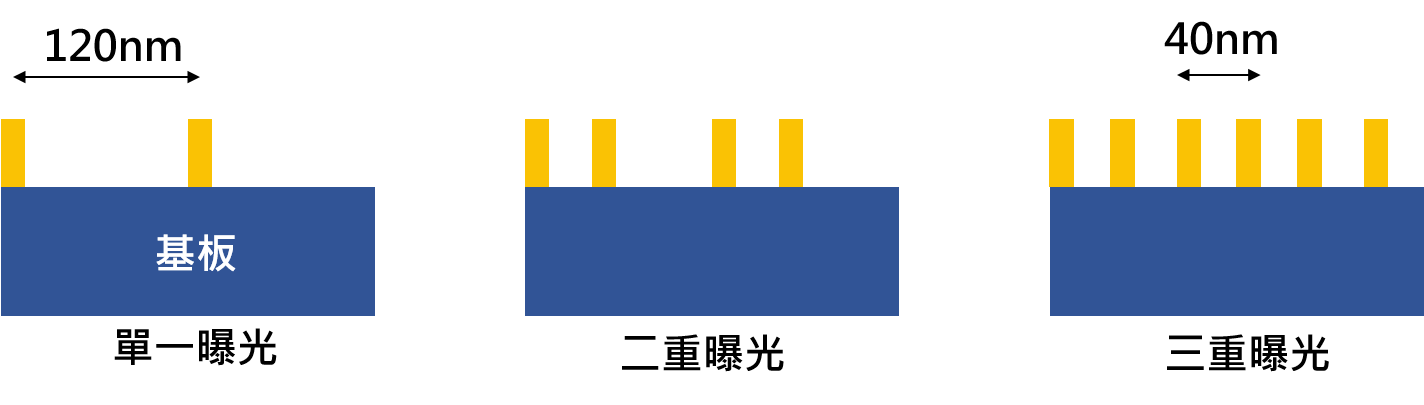

除了上述的浸潤式蝕刻技術,面對當今10奈米以下的節點,半導體製程有兩大重點:多重曝光和極端紫外光(EUV),兩者的概念都相當直觀。如圖二所示,原本製程極限為120奈米(即兩個相同的元件最近距離為120奈米)。若使用相同的光罩和光源重複曝光蝕刻三次(三重曝光triple patterning),但每次都移動一點位置,就能製作出40奈米的結構,為原本極限的三分之一!不同的製程有不同的曝光次數,而這樣的方法被通稱為「多重曝光」。

●極端紫外光(Extreme Ultraviolet, EUV)

另一個重點則是重新回到歷史輪迴,使用更小波長的光──極端紫外光。波長193奈米的紫外光在曝光蝕刻技術中已經行之有年,現在正是往更低的波長走下去的時候了。不同於193奈米的「正常」紫外光,半導體設備商目標利用波長極短的「極端紫外光」,僅有數十奈米。若開發成功,這種光源搭配浸潤式蝕刻和多重曝光等技術,半導體能輕易走過次十奈米、甚至次奈米半導體節點。

儘管極端紫外光有強大的奈米結構製造能力,若要把它納入半導體製程,必須將現有的設備進行大改造,需要大量資金和時間才能投入實戰。目前許多半導體廠商把多重曝光當作短期研發項目,而極端紫外光則是列入長期目標。芝加哥大學和麻省理工學院科學家發展一種自組裝的方法,能夠使用現有的設備,卻大幅降低電子元件尺寸[參2]。

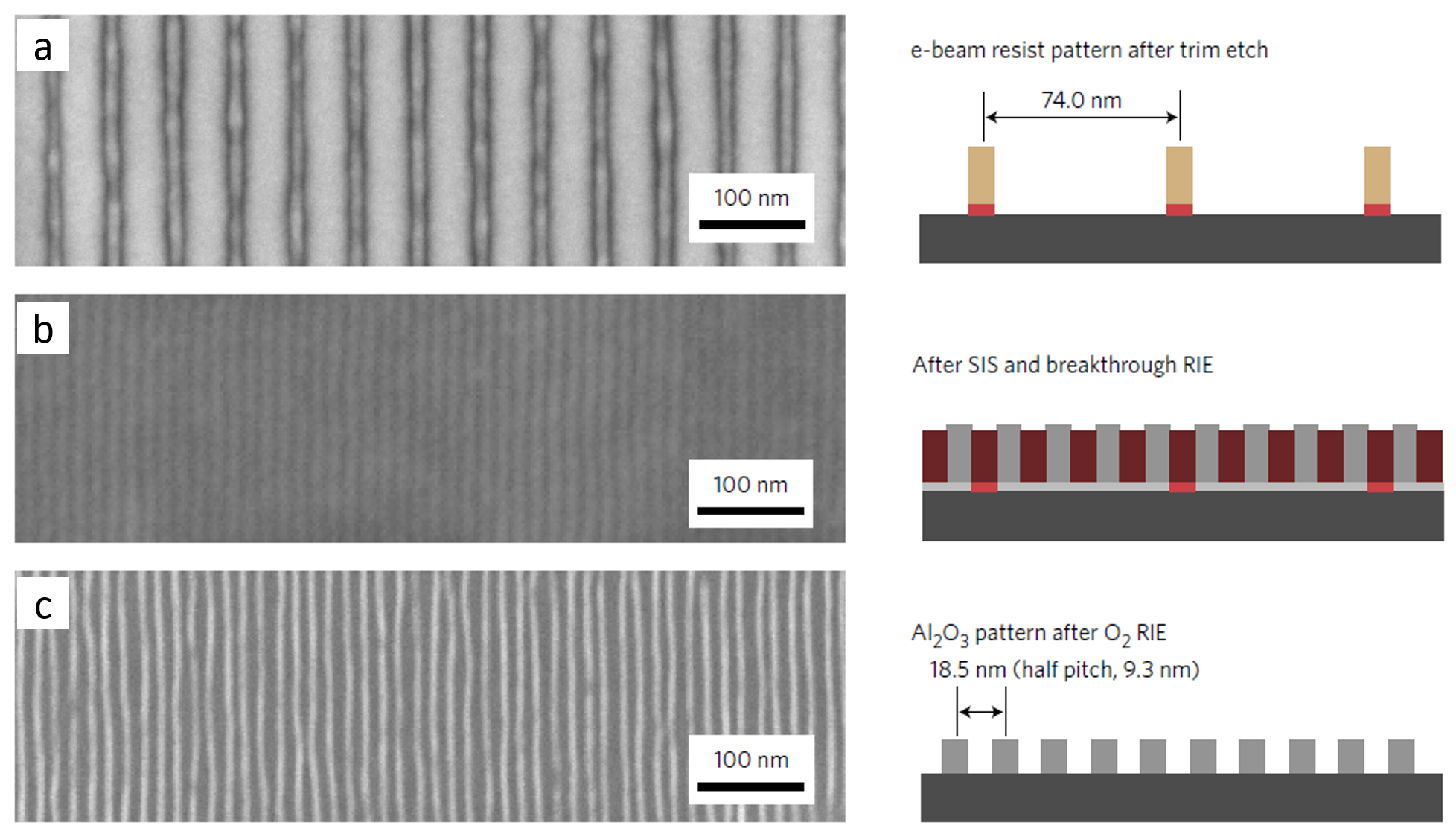

如圖三所示,首先在基板上透過傳統蝕刻方式長出間隔較大的結構(圖三a,間隔74奈米)。接著在基板上合成聚合物 [註],並且加熱處理。這些聚合物會進行特殊的化學交互作用,自動對齊成為比原來小四分之一的結構(圖三b)。最後,只要將不需要的部分清洗掉就完成了(圖三c)。透過這樣方法,使用74奈米的曝光顯影製程,就能製造出18.5奈米的電路結構,相當於9.3奈米的製程。這種方法看似和多重曝光很類似,但它利用的是分子的化學特性,不受光罩限制,可以達到更小的尺寸。

也許你會好奇:2017年的半導體節點已經是10奈米的製程了,製作出9.3奈米的結構對未來有幫助嗎?在半導體發展的初期,「xx奈米節點」中的「xx奈米」確實指的是最小的邏輯電路結構間距。但是到了近十年,製造商在基礎科學和電路設計上下了許多功夫,縮小電子元件的尺度已經不是在單位面積中製作更強電路的唯一方法。只要科技和製造技術進步到了一定的程度,我們就將這些技術取一個新的名字──「xx奈米節點」。也就是說實際上10奈米製程,是計算能力和10奈米的半導體相當,但實際上的尺寸約30多奈米 [參3]。根據國際半導體技術藍圖,2021年的3.5奈米製程,其邏輯電路間距也有16奈米,自組裝技術的9.3奈米可說是綽綽有餘。

[註] 聚合物包含(2-vinylpyridine)-b-polystyrene-b-poly(2-vinylpyridine),簡稱VSV ;poly(divinylbenzene),簡稱p(DVB)。

[參1] S. Borkar, “Design challenges for gigascale integration,” presented at the 37th IEEE/ACM Int. Symp. Microarchitecture, Portland, OR, 2004.

[參2] Hyo Seon Suh, Sub-10-nm patterning via directed self-assembly of block copolymer films with a vapour-phase deposited topcoat, Nature Nanotechnology (2017)

[參3] Barry Pangrl, A Node By Any Other Name, Semiconductor Engineering (2014)

--

作者:陳奕廷,台大物理系學士,史丹佛大學應用物理系博士班就讀中。