什麼是矽光子?(2)——從電子街道到光子高架橋

當矽光子被視為解決資料傳輸瓶頸的「光速捷運」,其實背後仍有不少工程挑戰待克服。本文延續前篇「資訊城市」的比喻,進一步解析矽光子在雷射整合與封裝上的瓶頸,包括材料不相容造成的熱應力與光耦合困難。台積電的 CoWoS 技術雖提供了階段性解方,卻非終點,未來更需朝「共同封裝光學元件」(CPO) 邁進,這是一場從「臨時轉運站」走向「高效交通整合」的革新之路。

撰文|黃鼎鈞

在上一篇文章中,我們將電腦比喻為一座資訊城市,指出傳統電子元件就像汽車在城市中塞車,而矽光子就像高速的光速捷運,能以光傳遞訊號、解決資料傳輸瓶頸。這條光速公路不只已開通,更吸引全球科技巨頭紛紛投入建設,但它真的已準備好全面取代傳統電子嗎?這一篇文章,我們將一探矽光子真正面臨的「路障」,也就是那些在發展矽光子科技時所遇到的技術瓶頸。

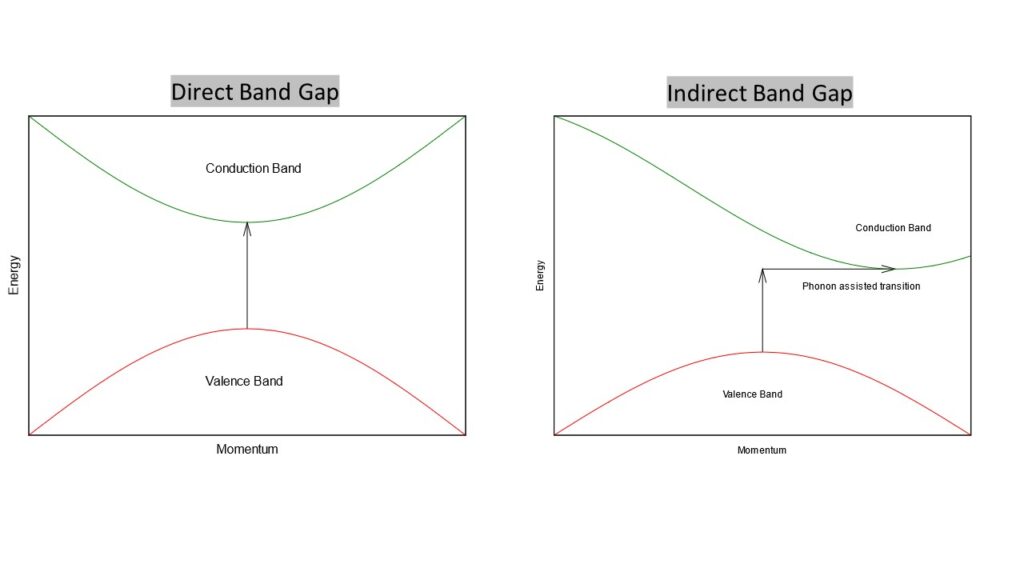

矽不能自行發光

前篇提到,矽屬於「間接能隙半導體」,當電子從導帶躍遷到價帶時,需藉由晶格振動釋放聲子,不像「直接能隙半導體」,可以直接透過發射光子釋放能量,因此矽本身並不容易發光。換句話說,雖然我們能夠在矽晶片上製作光波導、調變器與偵測器,但光源本身(雷射)仍必須由其他材料製成,並額外整合進晶片。目前常見的作法,是利用 III-V 族半導體製成雷射(例如磷化銦 InP),這類材料大多具備直接能隙,因此當電子能階躍遷時,能直接以光的形式釋放能量,適合用於雷射發光。為了將這些發光材料與矽基平台結合,工程師透過「異質整合」的技術,將不同材料(如 III-V 材料與矽)接合在一起,讓它們能在同一晶片上協同工作。

元件封裝困難

不過,說來容易,這卻是矽光子元件製程的困難所在,因為整合的過程牽涉到晶格常數、熱膨脹等物理性質的不匹配,就像是把不同材質的鐵軌接起來,一條會熱脹冷縮很多,一條則幾乎不變,當火車高速通過時,接縫處容易鬆動甚至變形,最終影響整體運作的穩定性。實際上,這些物理不匹配可能導致材料間產生應力集中、晶體結構裂痕,甚至在長時間使用後造成元件退化或效率下降,特別是在雷射與矽波導耦合的區域,容易出現光損失與信號不穩等現象。這些現象說明了: 異質材料整合並非只是將不同材料堆疊,更是材料科學與精密製程的重大考驗。因此,在矽光子元件的封裝上,也有著比傳統電子元件更高的門檻,電子訊號是透過金屬線來傳遞,然而,光的傳輸則嚴格要求光波導的角度與位置,一旦這些布局有些微的錯位,訊號就會大幅的損耗。

資訊城市的臨時轉運站-中介層

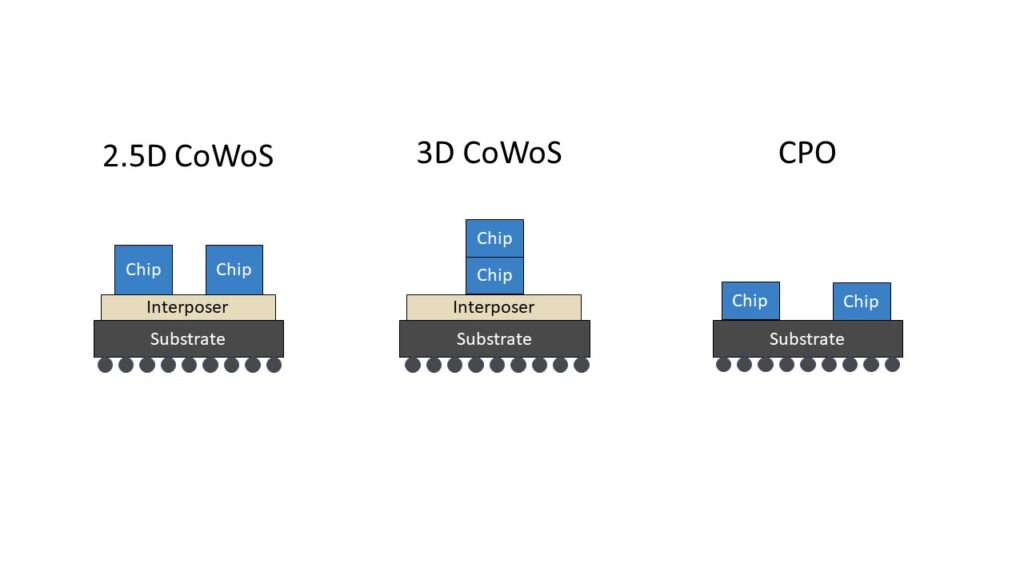

目前業界如何克服矽光子元件的封裝困難呢?台積電目前推出一種新進的異質整合封裝技術,稱為 CoWoS(Chip-on-Wafer-on-Substrate)。在這項技術中,工程師將多個晶片,例如邏輯晶片、記憶體晶片與光電晶片,先組裝到一塊具備精密連線的中介層(Interposer)上,再一同封裝到基板(Substrate)中。這種封裝方式就像在一座城市的現有交通網絡(如道路)上,興建一座多功能的轉運站,讓汽車、公車、捷運都能在同一平台整合運行。在這裡,光子就像捷運列車,需經過精確對位的轉乘站才能順利銜接不同路線。這樣的做法不但能緩解因材料熱膨脹係數不同而產生的應力,也降低了製程錯誤與耦合損耗的風險,進一步提高了封裝的穩定性與良率,讓矽光子得以真正嵌入晶片的資料交通主幹道。

然而,CoWoS 並非終極方案,更像是過渡階段的工程折衷,它固然大幅改善異質整合的封裝困難,但仍需額外的中介層與封裝空間,未來如果希望進一步縮小元件體積、提升能效,業界仍需探索「共同封裝光學元件」(Co-packaged Optics, CPO)等更為先進的整合架構,也就是將光電元件與邏輯晶片全部封裝於同一單元,取消中介層、拉近光源與訊號處理的距離,藉此降低功耗與延遲。就像城市的規劃一樣,或許我們能透過行人天橋、高架橋、地下道改善運輸,但最終還是希望能將交通全面整合,實現既高效又簡潔的未來城市樣貌。

參考文獻

- Siew, S. Y., Li, B., Gao, F., Zheng, H. Y., Zhang, W., Guo, P., ... & Lo, G. Q. (2021). Review of silicon photonics technology and platform development. Journal of Lightwave Technology, 39(13), 4374-4389.

- Ye, W. N., & Xiong, Y. (2013). Review of silicon photonics: history and recent advances. Journal of Modern Optics, 60(16), 1299-1320.

- Hu, Y. C., Liang, Y. M., Hu, H. P., Tan, C. Y., Shen, C. T., Lee, C. H., & Hou, S. Y. (2023, May). CoWoS architecture evolution for next generation HPC on 2.5 D system in package. In 2023 IEEE 73rd Electronic Components and Technology Conference (ECTC) (pp. 1022-1026). IEEE.

- Schulz, A. S., Kozoˇn, M., Vancso, G. J., Huskens, J., & Vos, W. L. (2024). Strongly inhibited spontaneous emission of PbS quantum dots covalently bound to 3D silicon photonic band gap crystals. The Journal of Physical Chemistry C, 128(22), 9142-9153.