矽製程相容的二維半導體

■隨著科技的進步,電子裝置日漸縮小,功能卻能增加,這全都有賴半導體產業中的摩爾定律。然而,在傳統半導體架構中,尺寸上的縮小有物理上的極限,眼看摩爾定律的末日就要到了!因應這個問題,許多半導體研究機構致力研發新的科技,搭配上二維材料,部份地解決了縮小半導體尺度時會面臨的困難。然而這些材料和長久使用的半導體科技並不相容,無法真正投入應用。近日,科學家提出一種新穎的半導體製程,能夠製造原子級厚度的二維半導體。這個技術有望併入以矽為基礎、廣為使用的製程。

撰文|陳奕廷

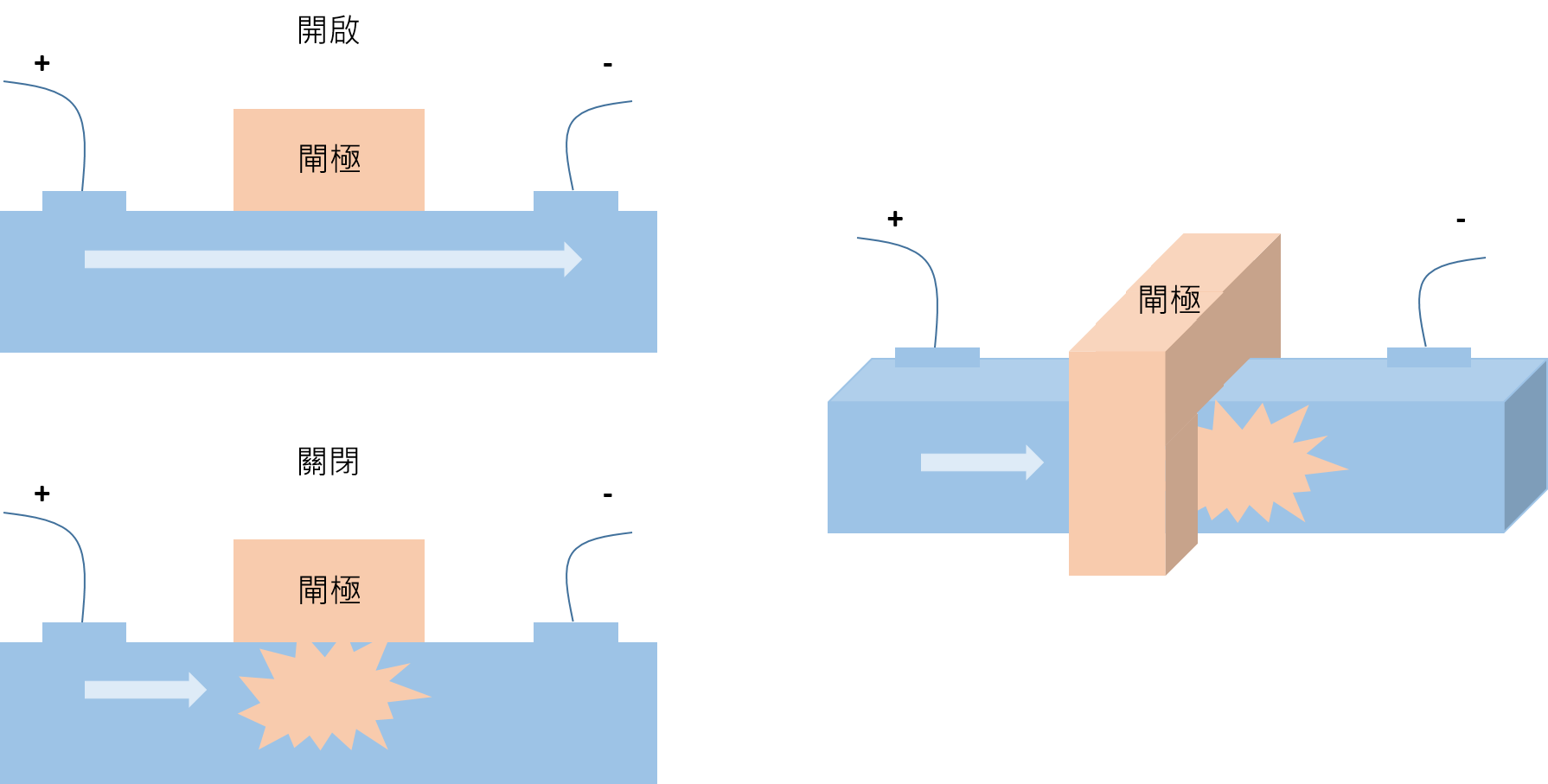

半導體最重要的應用之一是電晶體。電晶體的英文是「Transistor」可以被拆為兩個部份「trans-」和「-sistor」。前者字首代表改變,後者則是和電阻(Resistor)相關。從名字就能看出電晶體的功能:會改變的電阻。電晶體的電阻透過閘極(gate)被電訊號控制(圖一左),調控其通過的電流大小。換句話說,電晶體是一個「被電控制電開關」。電流的開關是邏輯電路最基本的原件,因此電晶體可說是電腦的基石。

●漏電流和鰭狀電晶體(FinFET)

一個優秀的電晶體,不同狀態之間的電流差異要越大越好,我們才能清楚的區分開啟和關閉。但隨著電晶體的尺寸越來越小,開和關的狀態越來越難分辨。其中一個原因是量子效應的作祟:在關閉狀態中,若電晶體兩端之間屏蔽的尺寸越來越窄,電子有越大的機會因為穿隧效應越過屏蔽。因此,本應關閉的電晶體有漏電流,無法有效關閉。

這個問體有一個簡單的解法:如果一個閘極無法好好關閉電晶體,你有試過兩個嗎?如圖一右所示,電子通道的上面、前面和後面都分別被閘極牢牢地包住,給電晶體一個滿滿的大閘極。這個結構叫做多閘極結構 (Multigate Structure),或因為長得像凸出來的魚鰭而又被稱為「鰭狀電晶體(FinFET)」。使用這種概念,我們能確保在持續縮小尺度時,電晶體仍然能有效地開啟和關閉。這個技術至今仍被半導體大廠,例如:台積電、Samsung、Intel等公司視為關鍵技術。

●散熱問題和二維材料

儘管我們能解決漏電流的問題,但仍有其他麻煩:散熱問題。隨著尺度縮小,電晶體在越小的空間內進行越多的運算。Intel公司曾說過,若單純比較能量密度,電腦晶片已經遠遠超越核能反應爐了。也就是說,電腦在運作時,源源不絕的熱量從CPU竄出。因此一個良好的晶片,必須搭配良好的散熱技術才能發揮功用。但是散熱效率有物理上的極限,無法隨著功耗的增加而無限量增強。

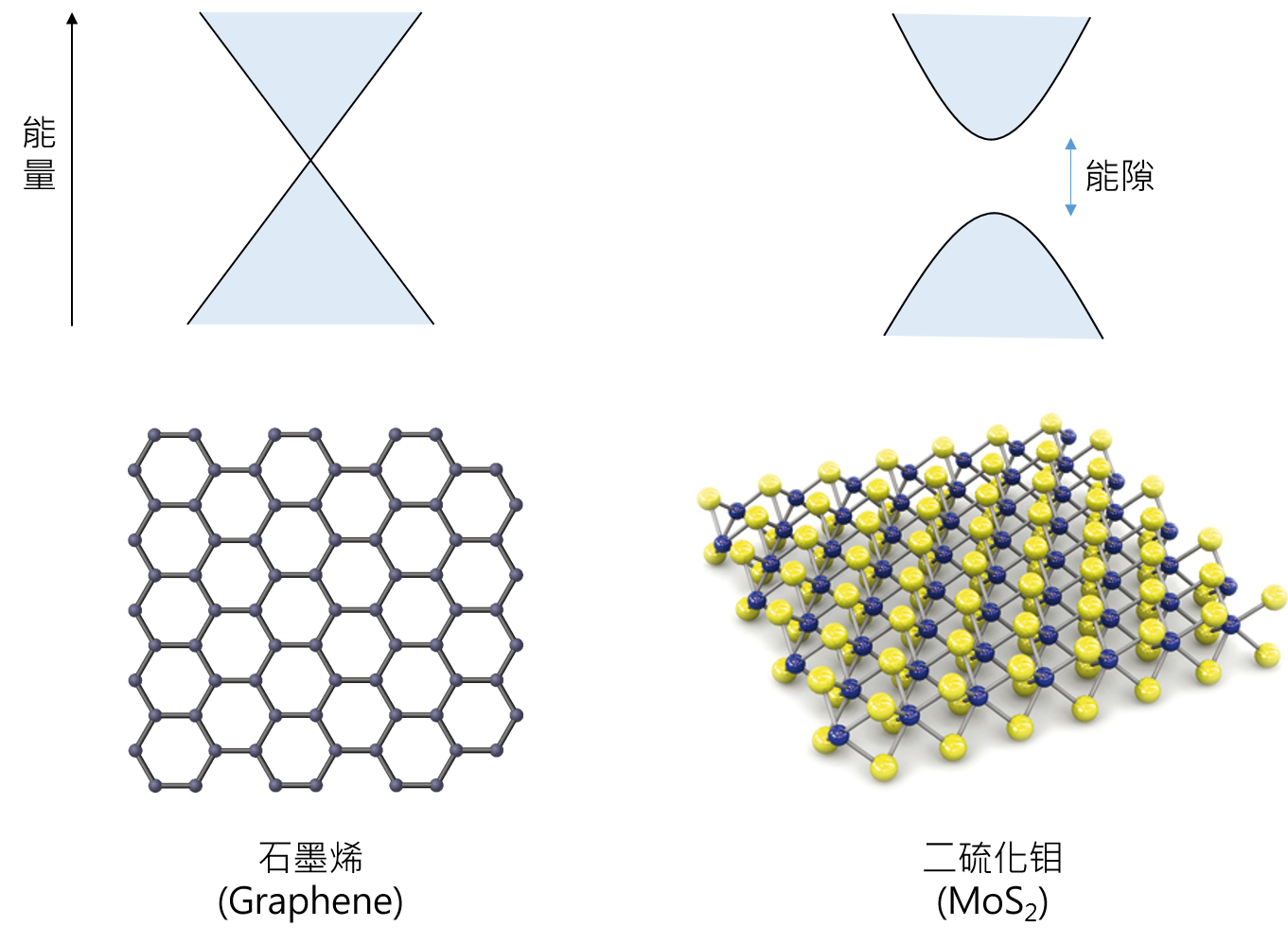

科學家尋找裡許多解法,其中一種是使用二維材料。最廣為人知的二維材料正是「石墨烯(Graphene)」,它與生俱來就有比較小的體積,並且有非常高的電子傳輸效率,若做成電晶體,應該能夠大幅減少廢熱和散熱問題。然而石墨烯不具備有半導體最重要的特性──能隙 (圖二左),因此在諸多應用中受限。其他類似石墨烯的材料被廣為研究,其中,二硫化钼(MoS2)是當今的主流。它同屬於二維材料,電子性質和石墨烯類似,但是它具有能隙。在許多研究中,科學家證明,二硫化钼和其類似的材料在許多方面表現能超越傳統的半導體。

●與矽半導體製程相容的二維材料

聽起來十分美好,但類石墨烯的二維材料(包含二硫化钼)都具備一項致命缺點。若要進行量產,必須能簡單快速的製備這些材料。為了大量製造類石墨烯材料,被廣泛使用的方法是「化學氣相沉積 (Chemical Vapor Deposition, CVD)」。在這個製程中,必須將材料加到非常高溫(攝氏500度甚至1000度以上)。在這個溫度,已經發展非常成熟的矽半導體科技完全不適用了。

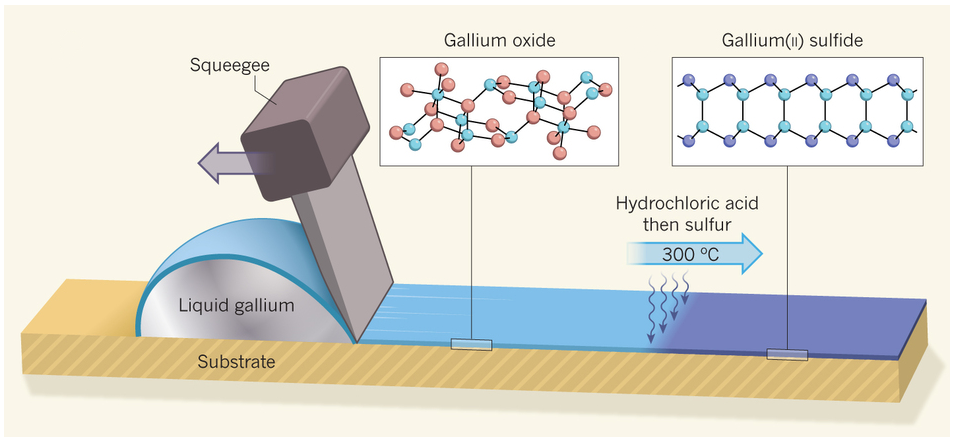

近日,澳洲科學家發明一種能低溫製備二維半導體的方法,過程直觀卻能製造單層晶格厚的材料。這個材料是硫化鎵(GaS),其製成有兩個重點:如何簡單地限制它在二維和如何將製成維持在低溫。首先,科學家在矽基板長上一層氧化膜,並將鎵金屬鋪上去。由於鎵金屬的熔點非常低(攝氏29.7度),在接近室溫的狀態下就能利用它的流動性將它平整地鋪在二氧化矽基板上(圖三左)。此時,最靠近表面氧化層的鎵金屬會產生鍵結。若把液態鎵刮掉,只有一層鎵金屬會被吸附在表面上,僅僅具有一層晶格的厚度(圖三中)。最後關鍵一步,若要在充滿硫氣的環境中直接把氧化鎵(GaO)變成硫化鎵),必須加熱到高達攝氏900度以上。科學家想到了一個巧思:先把氧化鎵在氯氣中變成氯化鎵,僅需加熱到300度,再以45度的低溫透過硫氣將氯化鎵轉換為硫化鎵(圖三右)。整個製程最高溫度僅有300度,和現有的矽半導體科技相容。

與矽半導體相容是一個很重要的特性。儘管二維材料能大幅改進以矽為基礎的部分元件,積體電路中許多元件目前仍然只能用矽實現。在先前的研究中,硫化鎵就被證明是一個在電晶體和光電裝置都具有許多應用的材料,如今又研發出與矽半導體相容的製程,我們又向電子裝置走向二維的日子前進了一大步。

參考資料:

Benjamin J. Carey et al., Wafer-scale two-dimensional semiconductors from printed oxide skin of liquid metals Nature Communications 8 14482 (2017)